# Implementation of Upper Voltage Control Circuit in Static NOR Gate & Domino NOR gate using Microwind

## K.Kalai Selvi

Faculty of Electronics & Communication Engineering, Government College of Engineering, Tirunelveli, Tamil Nadu, India.

## Kalai Vani Kanagarajan Senior Lead Engineer-Design, Cerium Systems.

Abstract- Upper Adaptive voltage level circuit (UAVL) – with its control signal, can supply more dc voltage to the load in active mode & reduced voltage in standby mode is developed. This circuit reduces the power dissipation in electronics. The reduction in power dissipation decreases the leakage current. This circuit is implemented in DSCH & Microwind for 90 nm. The power consumption of upper adaptive voltage level circuit of Domino nor gate is 18% less than domino nor gate. The power dissipation of it is 18% less than domino nor gate

Index Terms - Upper Adaptive Voltage Level circuit (UAVL), Subthreshold leakage, Domino NOR, Domino NOR with AVL

## 1. INTRODUCTION

Domino style incorporates clk inputs to all gates. The operation of these gates is divided into 2 phases. The phases are precharge & evaluation . In the precharge phase gate outputs are charged to high level voltage because PMOS transistors are controlled by clock input which in this phase is low .In the evaluate phase, the outputs of the gate can conditionally change to low voltage level. The logic of the gate is implemented only with NMOS transistors those transistors dictate if the outputs will be connected to the low voltage level to be discharged or not.

## 2. RELATED WORK

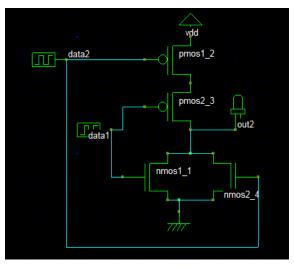

## 2.1 Static NOR gate

Depending on the inputs pmos & nmos is switched on or off. For example data1 & data2 are 01 respectively pmos2-3 is on , nmos1-1 is off & pmos1-2 is off & nmos2-4 is on .So there is no path for output to charged to Vdd & consequently output is low.

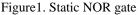

## 2.2 Domino NOR gate

Domino circuit works in 2 phase, during precharge state i.e when clkdomino is low pmos is charged so that output is high driven to Vdd, during evaluate phase i.e clkdomino is high nmos is turned on for example when 01 is given to data1 & data2 respectively nmos1\_3 is in off state & nmos2\_2 is turned on so output is pulled down to 0 volt through nmos switches. This logic works in evaluate phase

Figure 2. Domino NOR gate

## 3. PROPOSED WORK

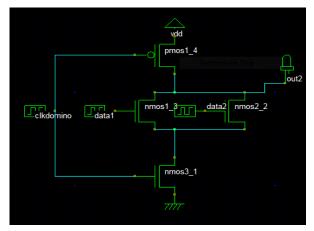

3.1.UPPER ADAPTIVE VOLTAGE LEVEL CIRCUIT (UAVL)

Figure 3. Upper Adaptive Voltage level circuit (UAVL)

An UAVL circuit, in general, consists of a single PMOS switch and m weakly connected Nmos switches connected in series . Here m=2 is considered. When load circuit is in active mode ,pmos of UAVL supplies Vdd to load & n-SWS is turned off. In standby mode 2 nmos of UAVL is on & supplies reduced voltage i.e Vdsn.

Now, the drain volltage of load is

Vdsn = Vdd - 2v

v is voltage drop in single nmos. Hence, Vdsn is reduced which in turn increases the barrier height of the off-Nmos. Therefore Drain Induced Barrier Lowering (DIBL) effect is reduced and therefore the threshold voltage of the nMOS transistor is increased. This results in a decrease in sub-threshold leakage current of the nMOS transistor in the load circuit.

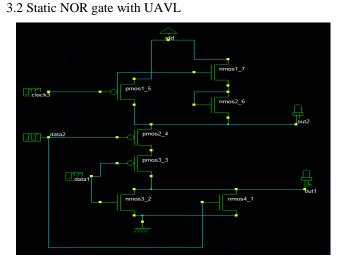

Figure 4. Static NOR gate with UAVL

UAVL supplies Vdd in active mode of load. Depending on inputs to nor gate output follows the logic operation.For example for inputs 01 respectively &clock3 in on condition UAVL supplies Vdd-2v through nmos1-7 & nmos2\_6 as data 2 is 1 pmos2-4 is off & nmos4-1 is on & data1 is 0 so pmos3-3 is on& nmos3-2 is off ,As there is no path from UAVL to out1 ,output is low.

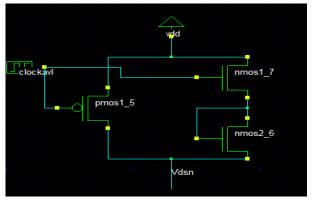

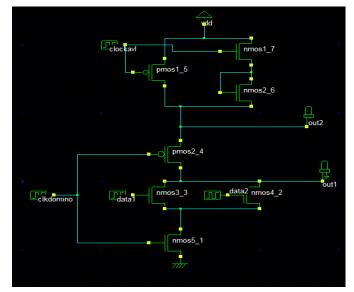

3.3. Domino NOR gate with UAVL

UAVL supplies Vdd to active load i.e when pmos2-4 is on it is the precharge phase so out1 is driven high.In evaluate phase nmos 5-1 is on & depending on inputs nmos switch remains on or off if on out1 is pulled down through nmos5-1 else it retains the charge.

Figure 5. Domino NOR gate with UAVL

## 4. RESULTS & DISCUSSION

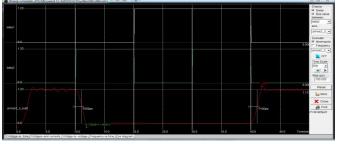

All the simulation results were obtained using Microwind & DSCH tool. The input sequence used is 00 01 10 11 respectively. Any circuit implemented with UAVL has low power consumption & power dissipation.

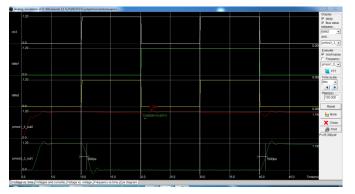

Figure 6. Static NOR gate -voltage curve & power consumption

Static NOR gate has power consumption of  $36.965 \mu$ W. Power dissipation is 0.037mW. Propagation delay is 1050ps

| Voltage variation of vdd                                                                                                                                              |                                                                                                                              |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---|

| Capacit. Voltage Temp. M.Carlo                                                                                                                                        | Curve vs. spacing Data Array                                                                                                 |   |

| Voltage of node: vdd<br>Range From : 0.00 v<br>To : 1.20 v<br>Step : 0.20 v                                                                                           | vdd(V) power(mWatt)<br>0.000 0.037<br>0.200 0.000<br>0.400 0.004<br>0.600 0.014<br>0.600 0.019<br>1.000 0.028<br>1.200 0.037 |   |

| Measurement                                                                                                                                                           |                                                                                                                              |   |

| Rise delay from data1 to pmos: -<br>Fail delay from data1 to pmos2<br>Frequency of node pmos2_3_0<br>Dissipation<br>Crossitak Amplitude<br>Final voltage pmos2_3_out2 |                                                                                                                              |   |

| Measure on: pmos2_3_oL -                                                                                                                                              |                                                                                                                              |   |

|                                                                                                                                                                       | 4 ×                                                                                                                          | 1 |

| Start Analysis                                                                                                                                                        | 🗸 ок                                                                                                                         |   |

Figure 7. Static NOR gate power dissipation

4.2 Static NOR gate with UAVL

Static NOR gate with UAVL has power consumption of  $35.380\mu W$ . Power dissipation is 0.035m W. Propagation delay is 950ps

Figure 8. Static NOR gate with UAVL -voltage curve & power consumption

| 🐼 Voltage variation of vdd                                                                                                                                                                                                                 |                                                                                                                                  | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---|

| Capacit. Voltage Temp. M.Carlo                                                                                                                                                                                                             | Curve vs. spacing Data Array                                                                                                     |   |

| Capacit. Voltage Temp.   M.Carlo  <br>Voltage of node: vdd v<br>Range<br>From: 0.00 v<br>To: 1.20 v<br>Step: 0.20 v<br>Measurement<br>Rits delay from clk3 to pmos3_*<br>Frequency of node pmos3_3_0<br>Dissipation<br>Crossital Amplitude | Vdd(Y) power(mWatt)<br>(0.000 0.035<br>(0.400 0.010<br>6.600 0.010<br>(0.600 0.016<br>(0.800 0.020<br>1.000 0.020<br>1.200 0.030 | * |

| Final voltage pmos3_3_out1 *                                                                                                                                                                                                               |                                                                                                                                  |   |

| Measure on: pmos3_3_oL -                                                                                                                                                                                                                   |                                                                                                                                  |   |

|                                                                                                                                                                                                                                            | 4                                                                                                                                | * |

| h                                                                                                                                                                                                                                          | ,                                                                                                                                | - |

| Start Analysis                                                                                                                                                                                                                             | ✓ OK                                                                                                                             |   |

Figure 9. Static NOR gate with UAVL - power dissipation

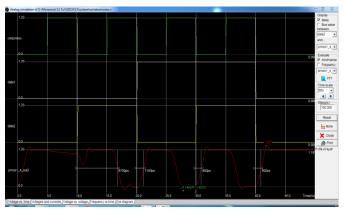

## 4.3 Domino NOR gate

Domino NOR gate has power consumption of  $59.414\mu$ W. Power dissipation is 0.059mW. Propagation delay is 3800ps

## Figure 10. Domino NOR gate -voltage curve & power consumption

| 🔯 Voltage variation of vdd                                                                                              |                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Capacit. Voltage Temp. M.Carlo                                                                                          | Curve vs. spacing Data Array                                                                                                |

| Voltage of node:<br>Range<br>From: 0.000 ∨<br>To: 1.20 ∨<br>Step: 0.20 ∨                                                | vdd(v) power(mWatt)<br>0 000 D056<br>0 400 0.007<br>0 600 0.007<br>0 600 0.016<br>0 800 0.027<br>1.000 0.024<br>1.200 0.059 |

| Measurement Crossilat Amplitude Final voltage pmos1_4_out2 Maximum did Current Power efficiency Measure on: pmos1_4_out |                                                                                                                             |

| Start Analysis                                                                                                          |                                                                                                                             |

Figure 11. Domino NOR gate power dissipation

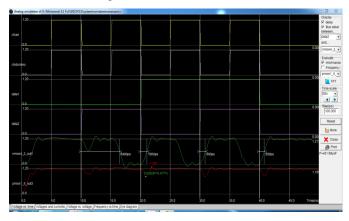

4.3 Domino NOR gate with UAVL

Figure 12. Domino NOR gate with UAVL- voltage curve & power consumption

| Voltage variation of vdd                                                                                                                                                                                         | Curve vs. spacing Data Array                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capacit. Voltage Temp. M.Carlo<br>Voltage of node: vdd v<br>Range<br>From : 0.00 v<br>To : 1.20 v<br>Step : 0.20 v<br>Measurement<br>Crosstalk Amplitude<br>Final voltage rmos4_2_out<br>Measure on: nmos4_2_ovv | vd(V)         power(mWatt)           0.000         0.48           0.200         0.006           0.400         0.011           0.600         0.22           0.800         0.027           1.000         0.337           1.200         0.048 |

| Start Analysis                                                                                                                                                                                                   | <b>у</b> ок                                                                                                                                                                                                                                |

Figure 13. Domino NOR gate with UAVL - power dissipation

Power consumption is  $48.198 \mu W$  . Propagation delay is 3700ps. Power dissipation is 0.048 m W .

| Parameters                      | Power<br>Consumpti<br>on<br>(µW) | Power<br>Dissipation<br>(mW) | Idd current at<br>node<br>(mA) | Delay<br>(ps) |

|---------------------------------|----------------------------------|------------------------------|--------------------------------|---------------|

| Static NOR gate                 | 36.965                           | 0.037                        | 0.376                          | 1050          |

| Static NOR<br>gate with<br>UAVL | 35.380                           | 0.035                        | 0.35                           | 950           |

| DOMINO<br>NOR                   | 59.414                           | 0.059                        | 0.395                          | 3800          |

| UAVL with<br>Domino NOR         | 48.198                           | 0.048                        | 0.393                          | 3700          |

5. SIMULATION RESULTS

#### 6. CONCLUSION

Upper Adaptive Voltage Level Circuit which reduces leakage power was developed. This circuit increases the threshold voltage which in connection reduces leakage power .So it can be used in low leakage power applications. It also has reduced power consumption & dissipation..

#### REFERENCES

- Pushpa Saini,Rajesh Mehra Leakage Power Reduction in CMOS VLSI Circuits, International Journal of Computer Applications (0975 – 8887) Volume 55– No.8, October 2012.

- [2] Rita Fariya ,T.Sai Baba, D.Lakshmaiah,Deign of Low power Domino Logic Circuits, International Journal of Technology and Engineering Science [IJTES]TM Volume 3[12], pp: 5156-5160, December 2015

- [3] Ms.Amrita Pahadia #1, Dr. Uma Rathore Bhatt Layout Design, Analysis and Implementation of Combinational and Sequential Circuits using Microwind, SSRG International Journal of VLSI & Signal Processing (SSRG-IJVSP) – volume 2 Issue 2 May to Aug 2015

- [4] Ankita Sharma, Divyanshu Rao, Ravi Mohan, Design and Implementation of Domino Logic Circuit in CMOS Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016)

- [5] Pushpa Raikwal, V. Neema, S. Katiyal LOW POWER WITH IMPROVED NOISE MARGIN FOR DOMINO CMOS NAND GATE International Journal Of Computational Engineering Research / ISSN: 2250–3005

- [6] Ankit Kori, Mohammed Arif Comparative Analysis of Domino Logic Circuits for Better Noise and Delay Performance International Journal of Engineering Trends and Technology (IJETT) – Volume 30 Number 3 - December 2015

#### Authors

K.Kalai Selvi completed M.E in Optical Communication at Alagappa Chettiar College of Engineering & Technology, Anna University. Working as Assistant Professor in Government College of Engineering ,Tirunelveli, Tamil Nadu. Has 12 years of teaching experience.

Kalai Vani Kanagarajan, Senior Lead Engineer-Design, Cerium Systems Has 14 years of Industrial Experience. Has worked in Arasan Chip Techologies, Posedge Technologies, HCL systems.